Groundbreaking Advances in CFET Technology Revealed at IEDM 2024!

2024-10-11

Author: Nur

Groundbreaking Advances in CFET Technology Revealed at IEDM 2024!

In the exciting landscape of semiconductor technology, the upcoming International Electron Devices Meeting (IEDM) in San Francisco, set for December 7 to 11, will showcase significant advancements in vertically-stacked complementary field effect transistors (CFETs). Researchers from leading firms including TSMC, IMEC, IBM, and Samsung are poised to present their latest findings.

One of the highlights will be TSMC's groundbreaking paper discussing the performance of a fully functional monolithic CFET inverter built on a 48nm gate pitch, which is comparable to the emerging 5nm process technology. This achievement marks an important step in the evolution of CFETs, which were first proposed by the IMEC research institute as a potential successor to traditional transistor architectures.

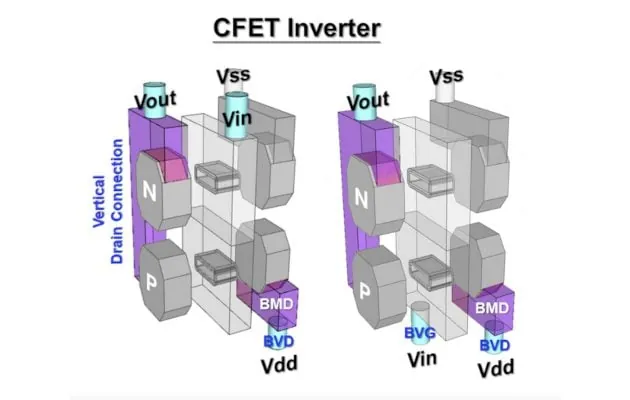

The paper, titled "First Demonstration of Monolithic CFET Inverter at 48nm Gate Pitch Toward Future Logic Technology Scaling," authored by S. Liao et al, emphasizes the innovative design of the inverter. It features a stacked configuration of n-type nanosheet transistors placed above p-type nanosheet transistors, integrating backside contacts and interconnects for enhanced performance and design flexibility. The performance metrics are impressive: the devices exhibit a voltage transfer characteristic of up to 1.2V and a subthreshold slope of 74 to 76 mV/V for both n- and p-type devices. Although this CFET technology is not expected to enter commercial manufacturing yet, it represents a critical milestone in transistor development.

Another significant presentation will come from IMEC on their research paper, "Double-Row CFET: Design Technology Co-Optimization for Area Efficient A7 Technology Node," which illustrates continuous advancements in scaling CFETs along both vertical (z-axis) and horizontal (x-y plane) dimensions. The A7 technology node is anticipated to follow the 1nm (A10) node, indicating that IMEC envisions CFETs achieving mainstream production by around 2032 with their roadmap suggesting innovations in future technologies.

On the other hand, IBM Research and Samsung will also introduce groundbreaking ideas. Their paper, titled "Monolithic Stacked FET with Stepped Channels for Future Logic Technologies," proposes a unique stepped channel structure, where the bottom FET channels are wider than those above. This design aims to reduce stack height and mitigate challenges associated with high aspect ratio processes.

The IEDM conference, an essential event in the electronics industry, promises to illuminate the path toward next-generation semiconductor technologies. With experts from around the globe expected to share their insights, this year’s meeting is set to be a pivotal moment for the future of CFET technology and chip design.

Join the conversation as we delve deeper into these advancements and what they mean for the future of computing!

Brasil (PT)

Brasil (PT)

Canada (EN)

Canada (EN)

Chile (ES)

Chile (ES)

España (ES)

España (ES)

France (FR)

France (FR)

Hong Kong (EN)

Hong Kong (EN)

Italia (IT)

Italia (IT)

日本 (JA)

日本 (JA)

Magyarország (HU)

Magyarország (HU)

Norge (NO)

Norge (NO)

Polska (PL)

Polska (PL)

Schweiz (DE)

Schweiz (DE)

Singapore (EN)

Singapore (EN)

Sverige (SV)

Sverige (SV)

Suomi (FI)

Suomi (FI)

Türkiye (TR)

Türkiye (TR)