インテルが新たなチップレット接続の標準化を計画、より小型のチップレットで性能向上を目指す

2025-03-10

著者: 葵

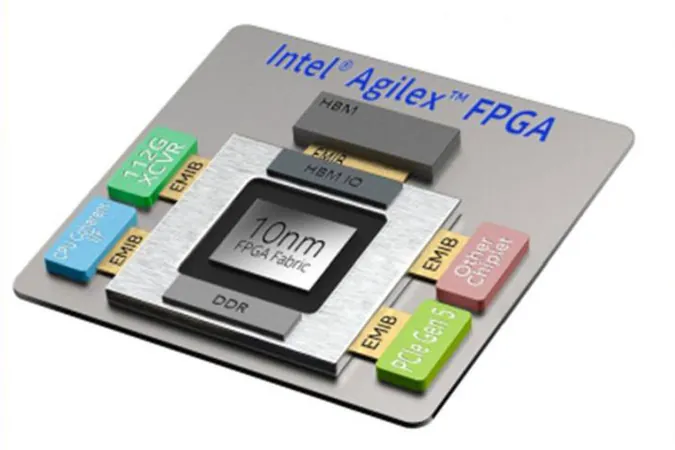

インテルは、2025年に予定されているISSCC(International Solid-State Circuits Conference)にて、最新のGranite Rapids-Dの発表を行う予定である。この技術革新に伴い、インテルは新たなチップレット技術の導入を進め、同時に接続性能の向上を考慮した設計を模索している。

今回の基調となる研究論文では、"300MB SRAM, 20Tb/s Bandwidth Scalable Heterogeneous 2.5D System Inferencing Simultaneous Streams Across 20 Chiplets with Workload-Dependent Configurations"というタイトルが付けられており、20個のチップレットを同時処理する能力について詳細に論じられている。

チップレット接続の標準化は、今後のコンピュータアーキテクチャにおいて非常に重要な仕様となると考えられている。これにより、より多くの機能を持つ小型のチップレットを組み合わせることで、性能を向上させることが可能になる。

過去の研究では、Tera-Scale Computingに関する開発が進められており、2007年のISSCCでは、80個のコアでTFlopsクラスの処理性能を示したことが記録されている。このような背景を持つ中で、インテルは新たに「Larrabee」という開発プロジェクトを立ち上げ、より効率的な処理を実現するための技術革新を追求している。

今後の目標として、接続するチップレットの種類や接続規格の対応を明確に定義し、これを普遍的にに活用できるようにすることが掲げられている。また、Inter chiplet networkや、基本ダイと上部ダイの共同設計に基づく標準化案が進められている。

このような動きにより、最終的には高効率かつ拡張可能なシステムが実現されることを目指しており、それによってインテルは市場の技術革新を牽引する姿勢を強化していく方針だ。これにより、今後数年での新たなコンピュータアーキテクチャの進展が期待されている。

Brasil (PT)

Brasil (PT)

Canada (EN)

Canada (EN)

Chile (ES)

Chile (ES)

Česko (CS)

Česko (CS)

대한민국 (KO)

대한민국 (KO)

España (ES)

España (ES)

France (FR)

France (FR)

Hong Kong (EN)

Hong Kong (EN)

Italia (IT)

Italia (IT)

日本 (JA)

日本 (JA)

Magyarország (HU)

Magyarország (HU)

Norge (NO)

Norge (NO)

Polska (PL)

Polska (PL)

Schweiz (DE)

Schweiz (DE)

Singapore (EN)

Singapore (EN)

Sverige (SV)

Sverige (SV)

Suomi (FI)

Suomi (FI)

Türkiye (TR)

Türkiye (TR)

الإمارات العربية المتحدة (AR)

الإمارات العربية المتحدة (AR)